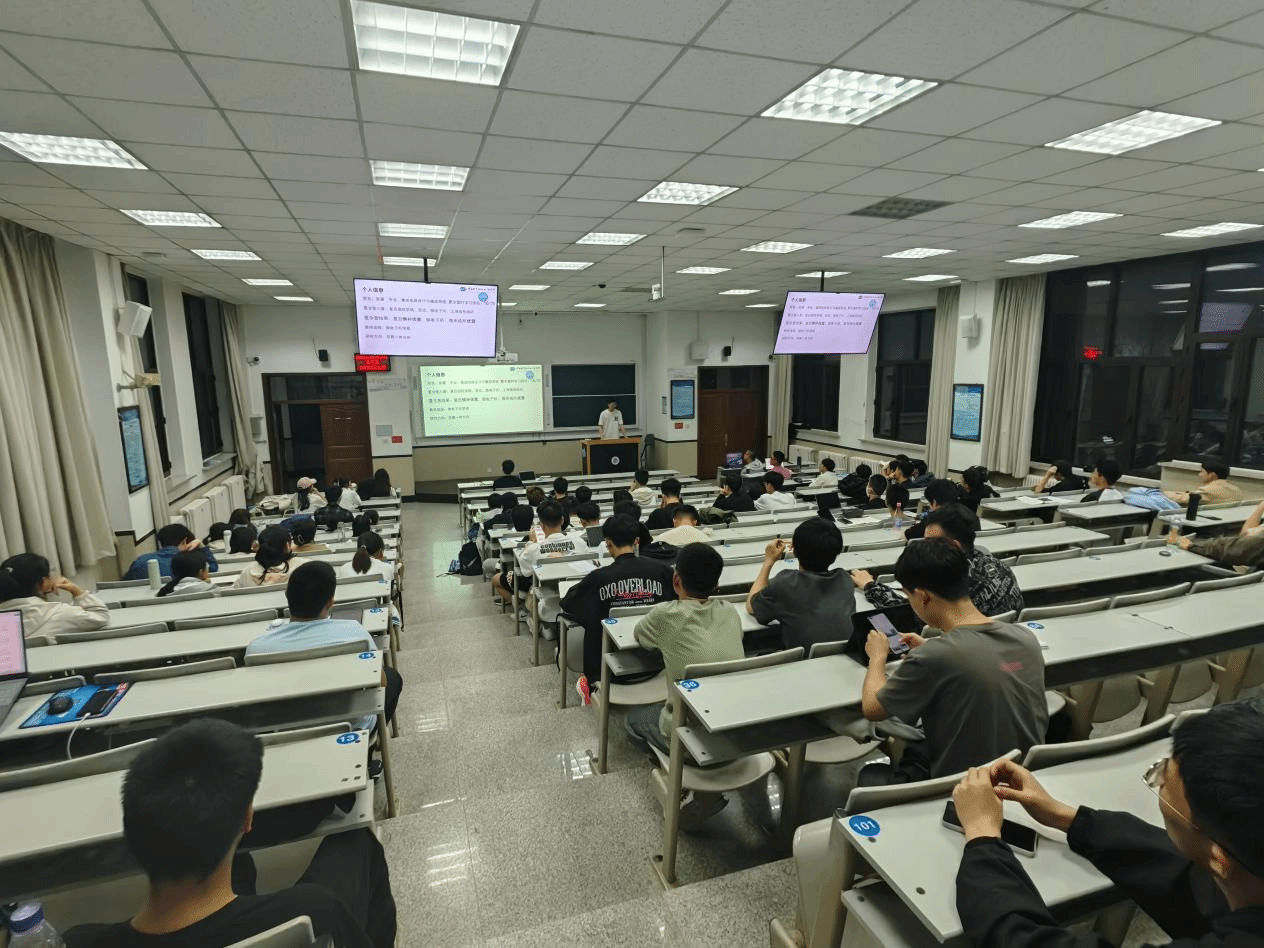

为探索EDA(电子设计自动化)技术在芯片设计中的核心作用,提升学生芯片设计自动化能力,1月中旬,集成电路学院“智绘芯图——EDA技术与芯片设计自动化”青年沙龙成功举办。活动吸引集成电路设计与集成系统、微电子科学与工程专业20余名学生参与,以“学生主讲+工具实操+案例研讨”的形式,打造了一场聚焦芯片设计核心环节的技术交流活动。

技术分享环节,我院EDA技术方向优秀学生代表带来专业解读。集成电路设计专业学长结合参与的省级创新项目,解析主流EDA工具链:“Synopsys的Design Compiler综合工具能实现时序优化30%,我们团队用它完成了一款8位MCU芯片的逻辑综合,面积利用率提升15%”;微电子专业学姐则聚焦开源EDA趋势,分享实践经验:“SkyWater PDK开源工艺库已支持130nm制程,我们基于KiCad和OpenLANE完成的CMOS反相器设计,通过了DRC(设计规则检查)和LVS(版图与 schematic一致性检查)”,干货满满的内容让现场同学专注记录。

工具实操与案例研讨环节互动频繁。同学们分组使用Cadence Virtuoso软件进行模拟电路版图绘制,结合《EDA技术及应用》《数字集成电路设计》课程知识,讨论布局布线对芯片性能的影响。案例分析中,大家深入剖析“华为海思用EDA工具链实现5nm芯片设计流程”“中芯国际基于EDA协同设计平台提升研发效率”等案例,探讨EDA技术在缩短设计周期、降低研发成本中的关键作用。有小组提出“基于开源EDA的低功耗传感器芯片设计思路”,其方案获得主讲学长点评:“开源工具组合虽有挑战,但能降低设计门槛,这个方向对学生创新很有意义”。

职业发展交流环节,“EDA行业人才需求”“芯片设计岗位技能准备”等话题引发热议。签约Cadence中国研发中心的学长分享感悟:“EDA企业特别看重算法优化能力,在校参与的时序分析算法改进项目,让我在面试中脱颖而出”;正在中科院计算所实习的学姐则建议:“想从事芯片前端设计的同学,要熟练掌握Verilog编程和UVM验证方法学,多做FPGA原型验证项目”。现场还设置了“EDA工具学习路径图”展示区,标注从基础工具到进阶应用的学习资源与时间规划。

活动负责人表示,此次沙龙旨在搭建EDA技术与学生实践的桥梁,未来学院将引入更多EDA企业正版工具授权,开展EDA设计竞赛与企业导师讲座。以芯为纸,以EDA为笔,这场聚焦芯片设计核心的青年沙龙,为同学们的专业成长注入了新动力。